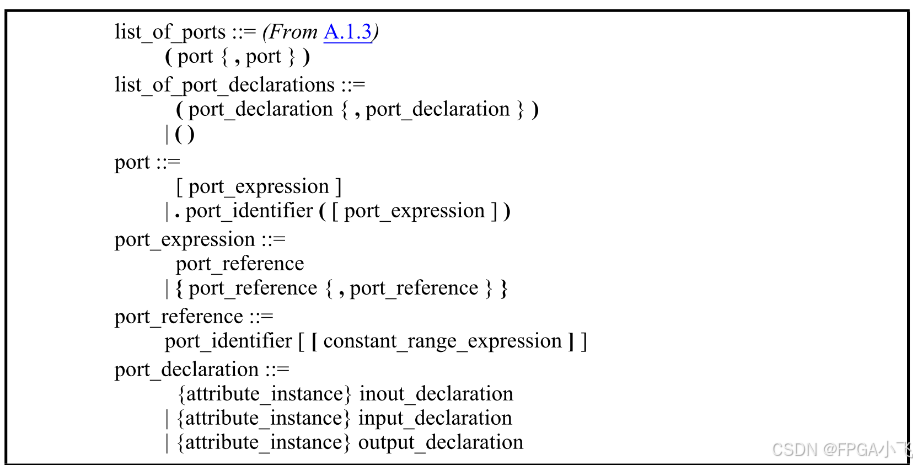

端口为由模块和基元组成的硬件描述提供了一种互连方式。端口/端口列表的标准语法如下表1所示:

表1:端口/端口列表语法定义

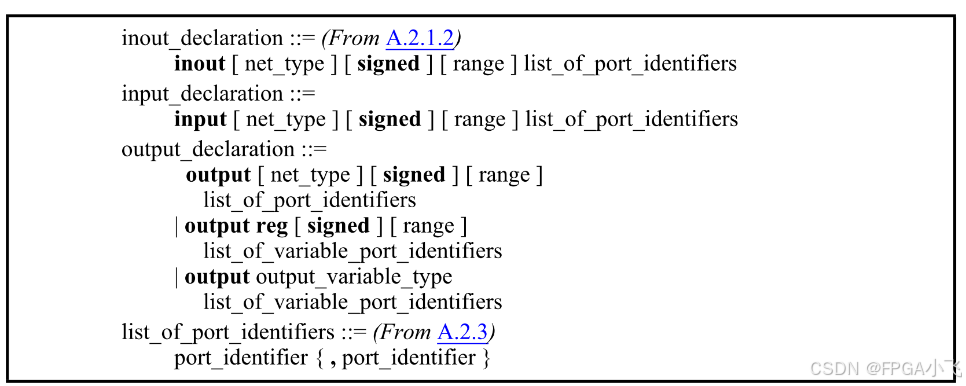

端口声明的语法如下表2所示:

表2:端口声明的语法定义

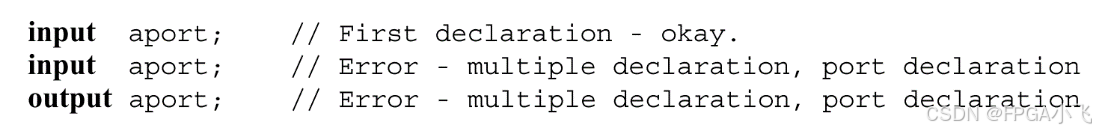

例子1:

有符号(signed)属性可以附加在端口port声明或相应的net或reg声明上,也可以同时附加在这两个声明上。如果端口或net/reg 被声明为signed,则另一个也应被视为signed。

隐式net应视为无符号net信号,连接到端口的net信号如果没有明确的有符号声明,则应视为无符号net信号,除非该端口被声明为有符号net。

例子2:

module test(a,b,c,d,e,f,g,h);

input [7:0] a; // no explicit declaration - net is unsigned

input [7:0] b;

input signed [7:0] c;

input signed [7:0] d; // no explicit net declaration - net is signed

output [7:0] e; // no explicit declaration - net is unsigned

output [7:0] f;

output signed [7:0] g;

output signed [7:0] h; // no explicit net declaration - net is signed

wire signed [7:0] b; // port b inherits signed attribute from net decl.

wire [7:0] c; // net c inherits signed attribute from port

reg signed [7:0] f; // port f inherits signed attribute from reg decl.

reg [7:0] g; // reg g inherits signed attribute from port

endmodule

module complex_ports ({c,d}, .e(f));

// Nets {c,d} receive the first port bits.

// Name 'f' is declared inside the module.

// Name 'e' is defined outside the module.

// Can't use named port connections of first port.

module split_ports (a[7:4], a[3:0]);

// First port is upper 4 bits of 'a'.

// Second port is lower 4 bits of 'a'.

// Can't use named port connections because of part-select port 'a'.

module same_port (.a(i), .b(i));

// Name 'i' is declared inside the module as an inout port.

// Names 'a' and 'b' are defined for port connections.

module renamed_concat (.a({b,c}), f, .g(h[1]));

// Names 'b', 'c', 'f', 'h' are defined inside the module.

// Names 'a', 'f', 'g' are defined for port connections.

// Can use named port connections.

module same_input (a,a);

input a; // This is legal. The inputs are tied together.

module mixed_direction (.p({a, e}));

input a; // p contains both input and output directions.

output e;

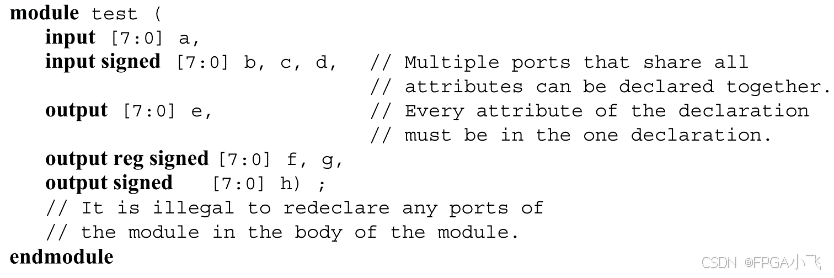

上面的例子中,端口的定义太冗杂,verilog标准提供了另一种非常简单的端口定义和声明方法,每个声明的port端口都提供了有关端口的完整信息。端口的方向、位宽、net或variable类型,以及端口是有符号sigend还是无符号unsigned,都有完整的描述。例子如下:

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起系统学习verilog最终标准IEEE Std 1364-2005吧!

1558

1558

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?