除了使用defparam外,为module实例中的参数赋值的另一种方法是使用“参数赋值”。该赋值方法有两种形式,分别是按顺序列表赋值和按名称赋值。这两种方式不得混用,对某一模块实例的参数赋值应完全按顺序或完全按名称进行。

1参数顺序列表赋值

参数顺序列表赋值应遵循模块内参数的声明顺序。使用此方法时,不必为模块内的所有参数赋值。但是,不能跳过一个参数而去给后面的参数赋值。因此,若要为模块内已声明参数的子集赋值,则构成该子集的参数声明应在不需要赋值的参数声明之前。另一种方法是为所有参数赋值,但对不需要新值的参数使用默认值(与模块定义中参数声明的值相同)。

例如:请看下面的例子,module实例 mod_a 、mod_c 和 mod_d 中的参数在例化过程中发生了变化:

module tb1;

wire [9:0] out_a, out_d;

wire [4:0] out_b, out_c;

reg [9:0] in_a, in_d;

reg [4:0] in_b, in_c;

reg clk;

// testbench clock & stimulus generation code ...

// Four instances of vdff with parameter value assignment by ordered list

// mod_a has new parameter values size=10 and delay=15

// mod_b has default parameters (size=5, delay=1)

// mod_c has one default size=5 and one new delay=12

// In order to change the value of delay,

// it is necessary to specify the (default) value of size as well.

// mod_d has a new parameter value size=10,delay retains its default value

vdff #(10,15) mod_a (.out(out_a), .in(in_a), .clk(clk));

vdff mod_b (.out(out_b), .in(in_b), .clk(clk));

vdff #( 5,12) mod_c (.out(out_c), .in(in_c), .clk(clk));

vdff #(10) mod_d (.out(out_d), .in(in_d), .clk(clk));

endmodule

module vdff (out, in, clk);

parameter size=5, delay=1;

output [size-1:0] out;

input [size-1:0] in;

input clk;

reg [size-1:0] out;

always @( posedge clk)

#delay out = in;

endmodule

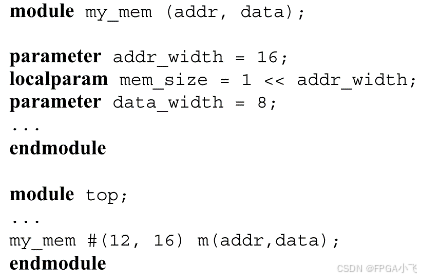

本地参数不能被改写,因此在参数值分配时,它们不被视为顺序列表的一部分。在下面的示例中,addr_width将被赋值为12,data_width将被赋值为16,mem_size 的值为4096。

2参数名称赋值

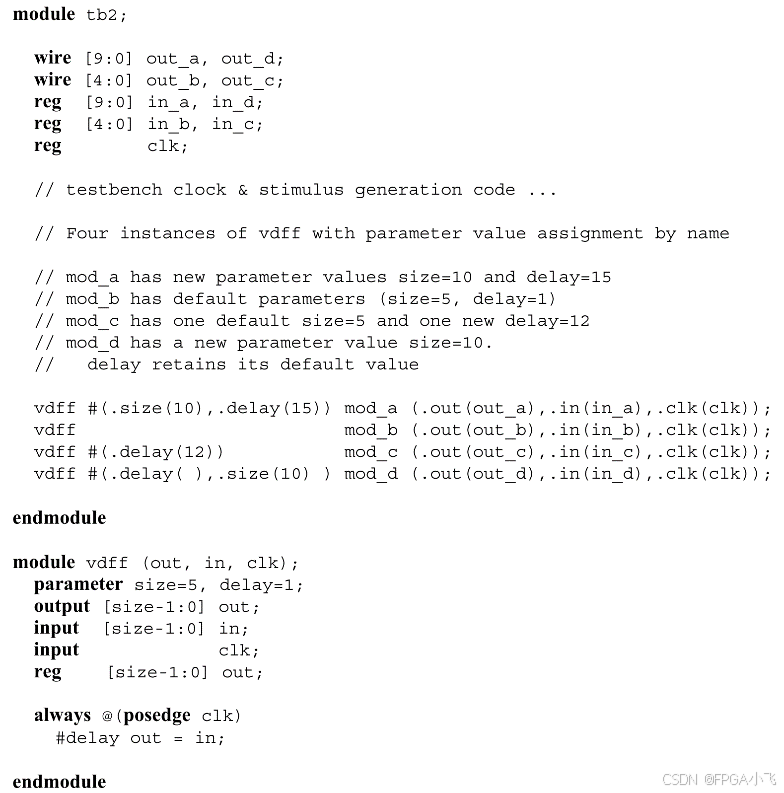

按名称改写参数值包括明确连接参数名称和新值,参数名称应为实例化模块中指定的名称。使用这种方法时,不必为模块中的所有参数赋值,只需指定改写新值的参数。新值参数表达式填充是可选的,这样实例化模块就可以记录某个参数的存在,而无需为其赋值,但括号是必需的,在这种情况下,参数保留其默认值。大家请看下面的例子,在实例化过程中,mod_a 的两个参数以及mod_c和mod_d的一个参数都发生了变化:

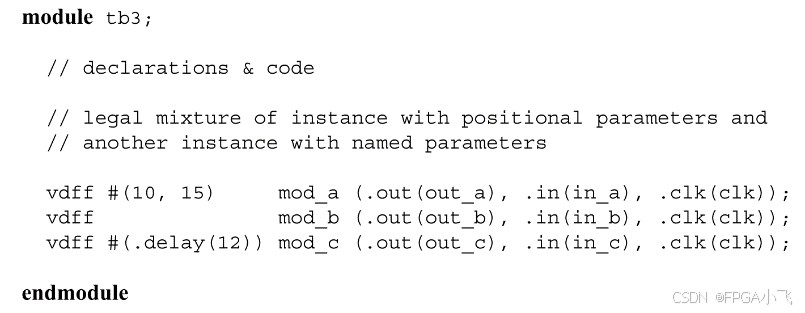

在同一个顶层模块中,使用不同类型的参数赋值方法来实例化模块是合法的。请看下面的例子,在实例化过程中,mod_a的参数是通过顺序列表进行参数重定义的,而mod_c的第二个参数是通过名称进行参数重定义的:

但是,如下面 mod_a 的实例化所示,使用按顺序和按名称重新定义的参数混合实例化任何模块都是非法的:

![]()

另外,一个parameter参数(例如 memory_size )可以用包含另一个parameter参数(例如 word_size )的表达式来定义。然而,无论是通过 defparam 语句还是在模块实例化语句中改写参数,新表达式都会替换参数定义。由于memory_size依赖于word_size的值,因此对word_size的修改会改变memory_size的值。例如,在下面的参数声明中,无论是通过 defparam 语句还是在定义这些参数的模块实例化语句中改写word_size参数值,都会自动改写memory_size。但是,如果通过 defparam 语句或实例化语句直接更新memory_size,那么无论word_size的值是多少,它都将使用该更新值:

parameter

word_size = 32,

memory_size = word_size * 4096;

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起系统学习verilog最终标准IEEE Std 1364-2005吧!

1443

1443

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?