好久没更,年也过了,各种节日也告一段落,今儿起,继续...

问题:

idea 中使用@Resource、@Autowire 出现红色波浪线

原因:

idea 默认进行了校验

解决方案:

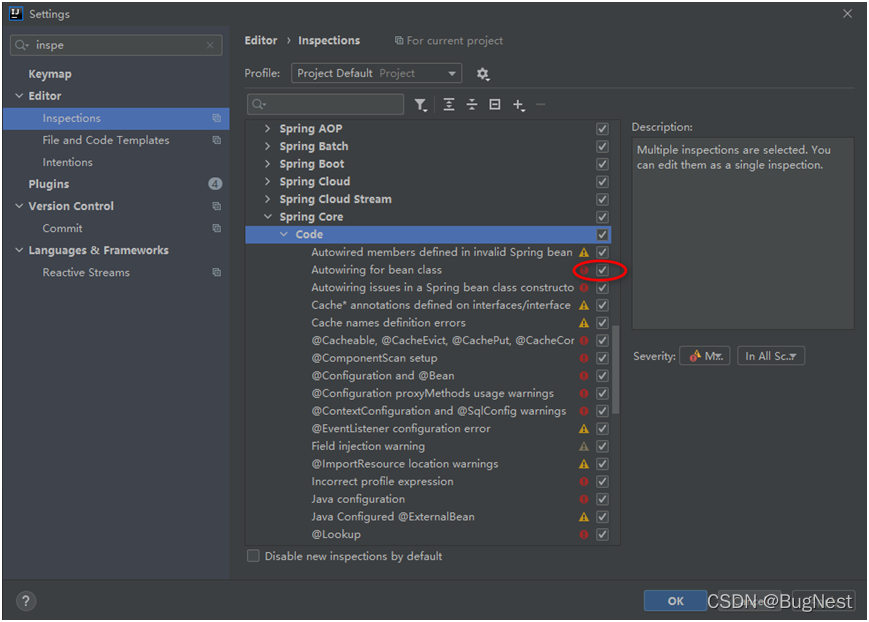

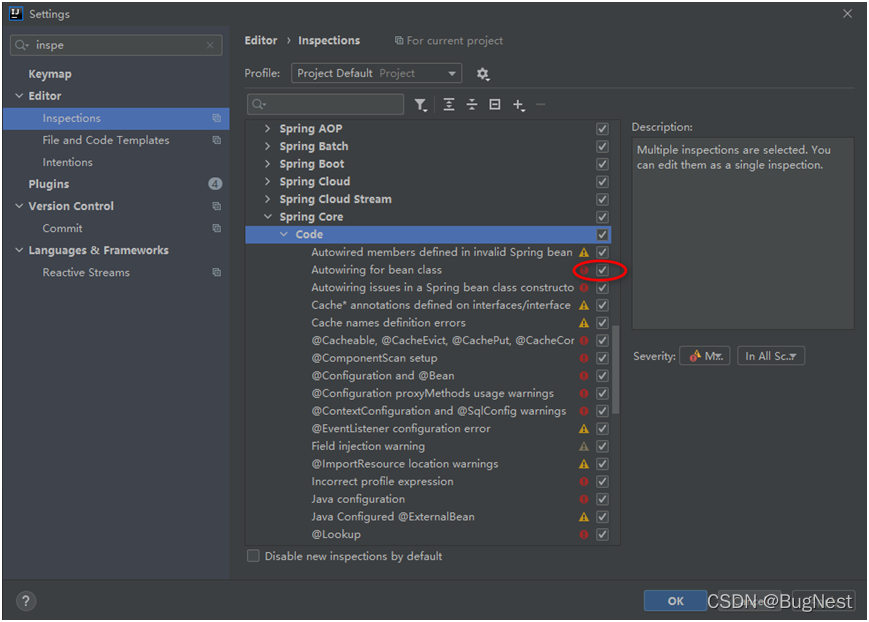

去掉校验,如图:

先来个开胃菜 ,本Bug到此为止,下个见.......

本文介绍了在IDEA中使用@Resource和@Autowired注解时遇到的红色波浪线问题,该问题是由于IDEA的校验设置导致的。解决方案是关闭相关校验。博客提供了一个简单的故障排除步骤,并预告了接下来的技术分享。

本文介绍了在IDEA中使用@Resource和@Autowired注解时遇到的红色波浪线问题,该问题是由于IDEA的校验设置导致的。解决方案是关闭相关校验。博客提供了一个简单的故障排除步骤,并预告了接下来的技术分享。

好久没更,年也过了,各种节日也告一段落,今儿起,继续...

问题:

idea 中使用@Resource、@Autowire 出现红色波浪线

原因:

idea 默认进行了校验

解决方案:

去掉校验,如图:

先来个开胃菜 ,本Bug到此为止,下个见.......

1673

1673

509

509

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?