在之前的几节里面,我讲解了系统初始化模块与验证系统初始化模块的代码。这样一来,围绕着系统初始化模块【sys_init】的代码,我就算是讲完了。讲完了以后,我们该去进行后续的代码的讲解了。

这个时候,请大家回到下述的链接,略微地回顾一下本项目的总体执行流程。

按照项目的执行流程,我们的这个系统,首先进行的,是系统的初始化。初始化完成之后,产生一个使能信号。这个使能信号的名字,叫做【init_done】。

初始化完成信号【init_done】,由【sys_init.v】代码文件产生,由控制中心模块文件【ctrl_center.v】接收。控制中心接收到了初始化完成信号以后,要产生本系统的第一个取指令使能信号。

本节,我们要去讲述的,就是从【sys_init.v】产生初始化完成信号,到控制中心【ctrl_center.v】产生第一个取指令使能的部分的代码。

还没有下载本项目的代码的,还请大家先将本项目的代码给下载下来。

大家可以点击上面的链接所指示的文章,在那篇文章里了解下载本项目代码的方法。

接下来,我们开始本节的讲解。

一. sys_init模块产生init_done信号

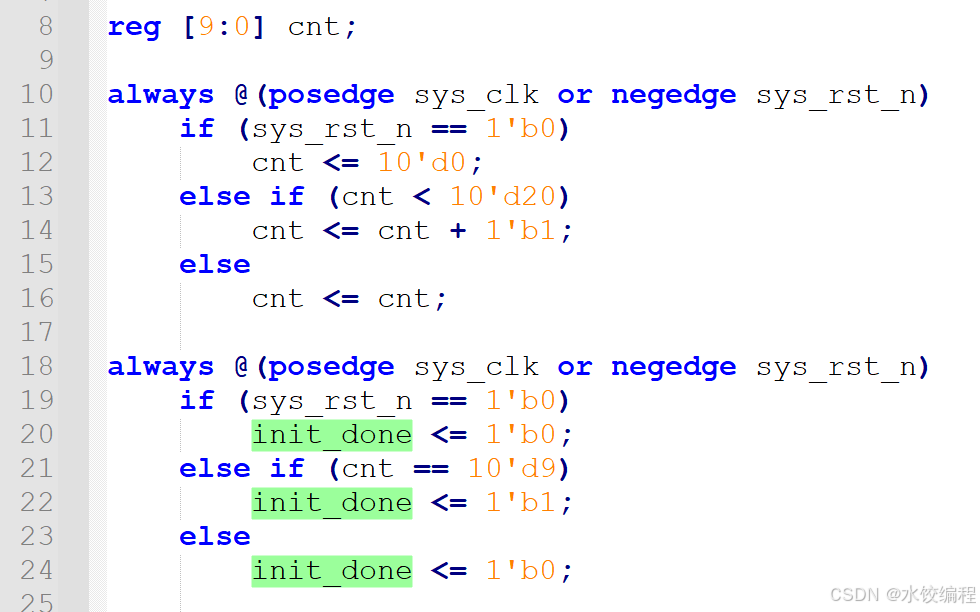

我们还是回到【sys_init.v】文件里面。这个文件,位于【cpu_me01\code\】路径里面。我们来看看这一文件的部分代码截图。

在【sys_init.v】的图1部分所示的代码里面,我们看到,里面是对cnt和init_done信号作出了处理。

首先来说cnt信号。它在系统复位信号【sys_rst_n】为低电平时,复位为0.当【sys_rst_n】为高电平时,则开始计数,每个时钟上升沿到来时,自身加1。当加到了20以后,一直保持此值不变。

当系统检测到【cnt == 9】的时候,init_done被非阻塞赋值为1,也就是产生一个高电平有效信号。其他时间,【init_done】为0。也就是,只有在系统检测到了【cnt == 9】的时候,init_done才会变为高电平,且仅仅维持一个时钟周期。

当【init_done】信号变为1的时候,我们就认为系统初始化完成了。

对于这里的init_done变为1的事情,我还想再来说一说,以便再次领着大家复习非阻塞赋值的知识。

非阻塞赋值,它是分为两个阶段。

非阻塞赋值的第一阶段,系统收集非阻塞赋值符号的右侧表达式所涉及的变量,并且计算右侧表达式的值。

非阻塞赋值的第二阶段,将右侧的表达式的值赋给左侧的变量。

比如下述代码

Res <= varA + varB;

我们假定,原本Res的值为0,varA的值为1,varB的值为2。

那么,在非阻塞赋值的第一阶段里,系统收集varA的值和varB的值,分别为1和2,并且计算【varA + varB】的值,为3。在第一阶段里面,仅仅是计算右侧表达式的值,但是左侧的Res变量依旧是原值0,并不会被赋予新的值3。在第二阶段,Res才被赋予新的值3。

我们回到图1的代码。假定一开始,【cnt == 8】且时钟信号处于处于高电平的稳定阶段。接下来,在下一个时钟的上升沿到来以后,【cnt】信号要变为9。

我们还是来说明一下这个变化过程。

初始条件:cnt == 8,且时钟信号处于高电平稳定阶段。

接下来,第1个时钟上

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1112

1112

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?